Our Editors-in-Chief’s Top Picks

The Editors-in-Chief of our CASS publications have selected some noteworthy papers from the recent issues of our journals:

IEEE Transactions on Circuits and Systems II: Express Briefs

1. R. Danesh, M. Safiallah, H. Pu and P. Heydari, “An Isolated Frequency Compensation Technique for Ultra-Low-Power Low-Noise Two-Stage OTAs”, IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 71, no. 1, pp. 6-10, Jan. 2024. doi: 10.1109/TCSII.2023.3298890.

https://ieeexplore.ieee.org/document/10195217

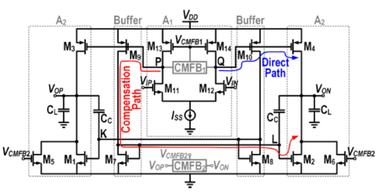

This paper proposes an isolated frequency compensation (IFC) technique for ultra-low-power (ULP) low-noise two-stage operational transconductance amplifiers (OTAs) with high gain-bandwidth (GBW) products. The proposed circuit achieves a 3 MHz of GBW and 2.3 V/ μs of average slew rate for a 45 pF capacitive load, while consuming a total current of 1.8 μA from a 1.8-V supply. The proposed circuit achieves a measured common-mode rejection ratio (CMRR) of ≥ 70 dB for a bandwidth of up to 100 kHz.

2. R. Shibata, Y. Hotta, H. Tabata and T. Iizuka, “Analysis of SAR ADC Performance Enhancement Utilizing Stochastic Resonance”, IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 70, no. 12, pp. 4324 - 4328, Dec. 2023. doi: 10.1109/TCSII.2023.3292318.

https://ieeexplore.ieee.org/document/10173546

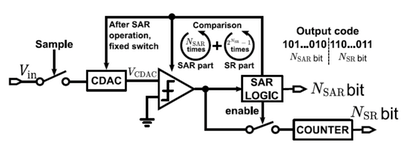

This paper proposes the use of stochastic resonance (SR) to a successive approximation register (SAR) analog-to-digital converter (ADC) to enhance its performance comparator’s performance. This scheme allows the use of a high-noise but low-power comparator in the SAR ADC, the total power consumption can be reduced even with the additional comparisons.

3. Y. Cui, L. Deng, K. Li and W. Shan, “FLC-EDC: A Fast Low-Cost Error Detection and Correction Scheme for AVFS System Based on Flip-Flops Resampling in 28-nm CMOS”, IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 71, no. 1, pp. 390-394, Jan. 2024. doi: 10.1109/TCSII.2023.3307401. https://ieeexplore.ieee.org/document/10226423

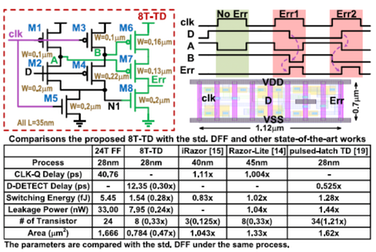

This paper presents a fast low-cost and wide-range timing management error-detection-correction scheme (FLC-EDC) based on resampling. An 8-transistor timing detector (8T-TD) with a fast response time of 12.35ps (only 30.3% of 24T DFFs) is proposed. A 28nm CMOS neural network accelerator chip across 0.45V−1.1V achieves 34.6%/48.7% power reduction and 43.8%/253.4% frequency gain at the super-/near-threshold (0.9V/0.55V) at the cost of 3.27% area overhead.

______________________________

CAll for Papers: TCAS-I Special Issue on Emerging Hardware Security and Trust Technologies

Manuscript submission deadline: 1 May 2024

Hardware security and trust have become a pressing issue during the last two decades due to the globalization of the semiconductor supply chain and ubiquitous network connection of computing devices. In addition to software, hardware circuits and systems are now an attractive attack surface for launching powerful cross-layer security attacks, allowing attackers to infer secret information, hijack control flow, compromise system root-of-trust, steal intellectual property, and fool machine learners. Hardware security threats can arise during various stages of the entire circuit life cycle, ranging from specification, design to fabrication and even recycling, which make the hardware security uniquely challenging.

The purpose of this special issue is to effectively convey the most up-to-date topics in the hardware security community. Topics of interest for this special issue lies in the introduction of most recent security attacks and threat models that are discovered in the hardware design and supply chain, emerging applications, as well as circuit theory, design methodology, design tools and implementations that help to thwart these threats. We sincerely hope not only this special issue can be a valuable reference for the target readers and researchers in the hardware security community, but also can motivate researchers in circuit and system design and in emerging technologies such as 5G/6G, IoT and artificial intelligence, to consider the new challenges and opportunities of incorporating an additional dimension of security into robust circuit and system design, testing, verification and implementation.

Hardware security is a fashionable research area in both industry and academy. Its scope is consistently growing. This special issue will include papers from extended version of AsianHOST 2023 and it also opens to public submissions related to emerging hardware security and trust technologies.

Authors are invited to submit Regular papers following the IEEE Transactions on Circuits and Systems I: Regular Papers (TCAS-I) guidelines within the scope of this Special Issue. Topics in scope for “Emerging Hardware Security and Trust Technologies” include (but are not limited to):

- Hardware-intrinsic security primitives (e.g., PUF and TRNG)

- Architectural and microarchitectural attacks and defenses

- Secure system-on-chip (SoC) architecture

- Post-quantum cryptography (PQC) implementation

- Trusted platform modules and hardware virtualization

- Side-channel attacks and countermeasures

- Hardware Trojan attacks and detection techniques

- Security analysis and protection of Internet of Things (IoT)

- Hardware IP core protection and trust for consumer electronics systems and IoT

- Security and trust of machine learning and artificial intelligence

- Automobile, self-drive, and autonomous vehicle security

- 5G and physical layer security

- Hardware-assisted cross-layer security

- Cyber-physical system (CPS) security and resilience

- Metrics, policies, and standards related to hardware security

- Security verification at IP, IC, and system levels

- Reverse engineering and hardware obfuscation

- Supply chain risks mitigation including counterfeit detection & avoidance

- Trusted manufacturing including split manufacturing, 2.5D, and 3D ICs

- Emerging nanoscale technologies in hardware security applications

Submission procedure:

Manuscripts should be prepared following the TCAS-I Information for Authors, which can be found here, and submitted through the IEEE author portal here.

Please choose the option “Special Issue on Emerging Hardware Security and Trust Technologies” in your submission.

Please note that papers submitted to TCAS-I are expected to be typically of 9-11 pages and no more than 14 pages in length in the two-column IEEE Transactions format. Please read the Information for Authors regarding mandatory overlength page charges beyond 11 pages.

Please be aware that the submitted paper will undergo the standard review process to ensure that all the contributions meet the high standards of the Journal. In this regard, if a conference paper has been previously published, your submission to this special issue must be a significantly more complete version of your conference contribution with appropriate addition of experimental data or other relevant verification. As a rule of thumb, you should add at least 70% more unpublished technical material. When submitting the extended journal version of your conference paper, you must disclose the original conference paper and attach a letter explicitly highlighting the additional contributions of the TCAS-I paper relative to the original conference paper.

Important dates

- 1 May 2024: Paper submission

- 15 June 2024: First-round review due

- 30 July 2024: Revised manuscript submission

- 20 August 2024: Second round review due

- 10 September 2024: Second (minor) revised paper submission

- 30 September 2024: Guest editor's final recommendation

- 15 October 2024: Final accepted paper submission due

- 31 December 2024: Expected inclusion in issue

Guest Editors:

- Qiang Liu, Tianjin University, China

- Weiqiang Liu, Nanjing University of Aeronautics and Astronautics, China

- Chongyan Gu, Queen's University Belfast, U.K

- Reza Azarderakhsh, Florida Atlantic University, U.S.A.

______________________________

Latest Tables of Contents of CAS Sponsored Journals

The latest issues of our CAS sponored journals have been published and the tables of contents can be accessed through the following links:

- IEEE Transactions on Circuits and Systems I: Regular Papers

- IEEE Transactions on Circuits and Systems II: Express Briefs

- IEEE Transactions on Circuits and Systems for Video Technology

- IEEE Journal on Emerging and Selected Topics in Circuits and Systems

- IEEE Circuits and Systems Magazine

- IEEE Transactions on Biomedical Circuits and Systems

- IEEE Design and Test Magaz

- IEEE Open Journal of Circuits and SystemsYongxiang Yo