IEEE Circuits and Systems Society Tour de France 2024: Celebrating 75 Years of Innovation

I. Introduction

The IEEE Circuits and Systems (CAS) Society France Chapter is excited to organize the "Tour de France" of Circuits and Systems in 2024, a celebratory event marking the 75th anniversary of the society. Inspired by the successful set of CASS Tours being organized in Region 9 since 2022, this event is a tribute to the sustained excellence and pioneering contributions of the IEEE CAS Society in the field of micro- electronics. Aimed at strengthening the future of French and European technological sovereignty, the tour provides a unique opportunity for students, educators, and industry professionals to explore the latest advances and network with leading experts in the field.

II. Event Overview and Societal Impact

Spanning six major French cities, each with a unique focus on various aspects of circuits and systems, this tour is crafted to disseminate knowledge, stimulate interest, and foster collaborations that transcend traditional academic and industry boundaries. Free for all attendees, the event underscores the society’s commitment to inclusive education and professional development, offering workshops, keynote speeches, and net- working sessions at no cost, including meals.

This detailed itinerary not only promises a comprehensive educational experience on various facets of circuits and sys- tems but also encourages meaningful interactions and collabo- rations, fostering a community of innovators ready to lead the next wave of technological advancements. The event attracted more than 215 attendees over a week, exceeding the number of French CAS members. The maillot jaune, Prof. Ricardo Reis, has "driven his bike" all around France to promote the CAS Society, delivering talks on his long experience in microelectronics and sharing his vision of the future challenges in circuits and systems.

Fig.1 (right): 6 cities, 5 subjects, 1 Maillot Jaune, 215 attendees, 36 talks

III. Detailed Itinerary and Key Highlights

A. Lille (16th April): Introduction to Microelectronics

The tour begins in Lille at JUNIA ISEN where Prof. Ricardo Reis led discussions on emerging trends in micro and nanoelectronics. The session explored how advances in semiconductor technology affect both consumer electronics and critical infrastructure, explaining the importance of microelectronics in enhancing national and global technological resilience. The day included a student poster session with interactive discussions, allowing attendees to interact directly with PhD students and professors in the field. More than 60 participants, most of them undergraduate students, enjoyed the event.

Fig. 2 (right): Students in Lille during presentation of Prof. Ricardo Reis

Program:

• 12:30pm – 1:45pm: Student Poster session with FREE pizza!!

• 1:45pm – 2:00pm: Welcome/IEEE presentation by Mathieu Chéne, IEEE Lille Student Branch

• 2:00pm – 3:15pm: Ricardo Reis (UFRGS Brazil) - Trends in Micro and Nanoelectronics

• 3:15pm – 3:40pm: Ricardo Reis: Why join IEEE CAS Society?

• 3:40pm – 4:00pm: Coffee

• 4:00pm – 5:30pm: Antoine Frappé and Benoit Larras (Junia - IEMN) - From the transistor to Artificial Intelligence

B. Bordeaux (18th April): Digital Pre-Distortion Focus

Bordeaux’s event at the Laboratoire IMS centers on Digital Pre-Distortion (DPD) technologies, critical for maintaining efficiency in modern RF communications. This session aimed to address the challenges posed by increased signal bandwidths and the need for power efficiency in communication systems. Through lectures and demonstrations, attendees examined the role of software-defined radios and neural network applications in developing more efficient DPD solutions.

Fig. 3 (left): Prof. Ricardo Reis and the students in Bordeaux

Program:

• 9:30am: Welcome

• 10:00am: Ricardo Reis - Trends in Micro and Nanoelec- tronics

• 10:45am: Maxandre Fellmann - Introduction to DPD

• 11:30am: Smail Bachir and Claude Duvanaud - Software- defined radio implementation of a low-cost and open source DPD for LTE/5G signals

• Lunch

• 2:15pm: Ricardo Reis - Why join IEEE CAS Society?

• 3:00pm: Germain Pham - Recent Advances in Power Amplifier Behavioral Modeling and Digital Predistortion using Neural Networks

• 3:45pm: Antoine Lhomel and Rémi Quéheille - Co- simulation Workflow for D-Band Power Amplifier Linearization using Walsh-based DPD

• 4:30pm: Maxime Guillot - IEEE Bordeaux Student Branch - CAS Chapter

C. Grenoble (19th April): Open Hardware Initiatives

The Grenoble stage delves into Open Hardware, hosted at Grenoble INP. The session, featuring a keynote by Prof. Boris Murmann from the University of Hawaii, discussed the potential of open-source ecosystems to revolutionize analog design. The day’s discussions also highlighted significant open hardware projects like the European Open Hardware Project and their impact on the accessibility and democratization of technology development. Panel discussions provided insights into the sustainability and future prospects of open hardware in academia and industry.

Fig. 4 (below): Prof. Ricardo Reis and the students in Grenoble

Program:

• 8:00am: Welcome / Badge

• 8:30am: Opening Keynote by Prof. Boris Murmann (University of Hawaii) - Re-Energizing Analog Design using the Open-Source Ecosystem

• 9:30am: Aurélien Nicolet (CIME-P) - The French plat- form supporting open hardware

• 10:00am: Krzysztof Herman (IHP): IHP Open Source PDK - sharing experience after one year of development

• 10:30am: Coffee

• 11:00am: 75th anniversary of CAS Society Keynote by Ricardo Reis

• 12:00pm: Lunch & Cocktail

• 2:00pm: Ricardo Reis (UFRGS) - Why join IEEE CAS Society?

• 2:30pm: Jean-Paul Chaput (LIP6 – Sorbonne University)

- Coriolis: The European Open Hardware Project

• 3:00pm: Coffee

• 3:30pm: Dr. Leonardo Gomes (TIMA - UGA) - The first 60 GHz circuit designed with open hardware platform

• 4:00pm: Deni Alves (UFSC) - ACM: a design-oriented model for open tools

D. Montpellier (24th April): Energy Constraints in Computing

Montpellier addresses the crucial topic of energy efficiency in computing at the Laboratoire d’Informatique Robotique et Microélectronique de Montpellier (LIRMM). This session focused on the need for low-power solutions across various computing platforms, from large-scale data centers to em- bedded systems in IoT devices. Experts like Michel Robert discussed emerging paradigms such as in-memory computing and their role in reducing the energy footprint of digital systems. The program included a guided tour of the CINES (Centre informatique national de l’enseignement supérieur), showcasing France’s efforts in sustainable computing infrastructure.

Fig. 5 (right): Visit of the CINES in Montpellier

Program:

• 10:15am: Welcome / badge

• 10:30am: Ricardo Reis - Power Optimization by Transis- tor Count Optimization

• 12:00pm: Lunch

• 2:00pm: Ricardo Reis - IEEE CASS and Opportunities

• 2:45pm: Paul Delestrac and David Novo - GPU efficiency in ML training

• 3:00pm: Jonathan Miquel and Laurent Latorre - Power- saving design methodology for embedded biologgers

• 3:15pm: Lila Ammoura, Marie-Lise Flottes, Arnaud Virazel, and Patrick Girard - Robustness of SRAM-based IMC Architectures

• 3:30pm : Bruno Lovison and Pascal Benoit - Study and design of MRAM-based in-memory computing architec- tures

• 3:45pm: Ismael Samaye, Gilles Sassatelli, and Abdoulaye Gamatié - Towards sustainable computing

• 4:00pm: Michel Robert - An introduction to CINES (Centre informatique national de l’enseignement supérieur) followed by a guided tour of the center

E. Paris (26th April): Hardware Solutions for AI

The final stop in Paris at Télécom Paris focuses on devel- oping hardware solutions that optimize AI applications. This session highlights the challenges associated with traditional computing architectures in AI and explores alternative ap- proaches that integrate memory and processing units to overcome the von Neumann bottleneck. Distinguished speakers, including Dongsuk Jeon from Seoul National University and Yiran Chen from Duke University, presented their research on novel hardware designs and efficient and robust AI-CAS.

Fig. 6 (below): Prof. Ricardo Reis and the students in Paris

Program:

• 9:00am: Dongsuk Jeon, Seoul National University DL IEEE SSCS - ”Designing an optimal hardware solution for deep neural network training”

• 10:00am: Kamel-Eddine Harabi, University of Paris Saclay - “Harnessing Memristor Variability for Edge Learning: From Theory to ASIC Implementation”

• 10:30am: Coffee Break

• 10:40am: Ricardo Reis, Federal University of Rio Grande do Sul - “Why join IEEE CAS Society?”

• 11:00am: Mikhail Manokhin, Telecom Paris - “Towards Flexible and Low-Power Wireless Smart Sensors: Recon- figurable Analog-to-Feature Conversion for Healthcare Applications”

• 11:30am: Ricardo Reis, Federal University of Rio Grande do Sul - “Power Optimization by Transistor Count Optimization”

• Lunch

• 2:15pm: Pietro Maris Ferreira, CentraleSupélec - “Energy Efficient and Edge Artificial Intelligence for IoT”

• 3:00pm: Zalfa Jouni, CentraleSupélec - “An Analog Spike-based Neuromorphic Sensor for Efficient RF Lo- calization”

• 3:00pm: Yiran Chen, Duke University DL IEEE CASS

- “Efficient and Robust AI-CAS Through Cross-Layer Optimizations”

• 4:00pm: Zulal Kiraz, Telecom Paris - “Non Sum- Separable Energy Systems Consideration for Equilibrium Propagation”

• 4:30pm: Discussions

IV. Special Acknowledgments and Collaborative Efforts

The tour is made possible through the collaborative efforts of the IEEE CAS France chapter, GDR SoC2 (the French academic network on microelectronics), and various academic and industry partners. Noteworthy contributions from insti- tutions such as Junia ISEN, the IEEE Lille Student Branch, Laboratoire IMS, the IEEE Bordeaux Student Branch, TIMA, the IEEE Grenoble Student Branch, LIRMM, and Télécom Paris have been instrumental in organizing the sessions. Prof. Ricardo Reis deserves a special mention for his leadership and continued contributions to the IEEE CAS community. His visit was very well appreciated in all the visited cities, and he motivated numerous people to subscribe to the CAS Society!

V. Conclusion and Future Prospects

As the "Tour de France" of Circuits and Systems 2024 concludes, the IEEE CAS Society looks forward to building on the success of this event to further enhance the field of mi- croelectronics. The tour not only celebrates past achievements but also sets the stage for future innovations that will continue to shape the technological landscape of France and beyond.

In closing, the organizers extend their heartfelt gratitude to all the speakers, participants, volunteers, and hosting venues for their dedication and enthusiasm. Their collective efforts have ensured the tour’s success and have significantly con- tributed to the vibrant and collaborative spirit of the IEEE CAS community.

The success of the Tour de France calls for a second round, inviting the maillot jaune Prof. Reis to take his bike in November 2024 with more stops! Come and meet him at the ligne d’arrive´e (arrival line) at ICECS 2024 in Nancy.

Contributed by

Francois Rivet, CASS BoG Member

Patricia Desgreys, CAS France Chapter Chair

Nathalie Deltimple, CAS France Chapter Co-Chair

Antoine Frappé, CAS France Chapter Treasurer,

Sylvain Bourdel, CAS France Chapter Secretary,

Laurent Latorre

_________________

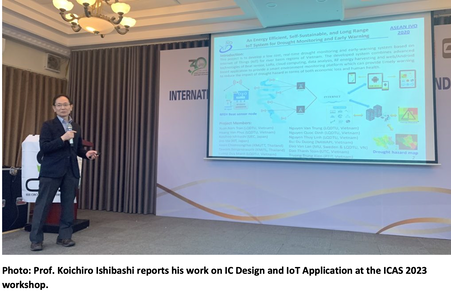

International Workshop on Integrated Circuits and Systems 2023 (ICAS 2023)

On the 8th November 2023, the IEEE Circuits and Systems Society (CASS) Vietnam Chapter has successfully organized an one-day events for the International Workshop on Integrated Circuits and Systems 2023 (ICAS 2023). Esteemed attendees from the CAS Society included Prof. Myung Sunwoo (President-elect), Prof. Yoshifumi Nishio (Vice President on Finance), Prof. Fakhrul Rokhani (Vice President on Education), and Prof. Ricardo Reis (Rio Grande do Sul CAS Chapter). This international workshop involves two sessions involving short-training courses for Students and a technical main workshop of ICAS 2023.

For the first event at Hoa Lac campus, more than 40 students attended brief lectures focusing on sharing experiences on IC design, using open-source tools in IC design, design library selection... This event provided an opportunity for students to learn from professors and experts in this field and gain practical insights on IC designs. These courses were designed to be concise yet comprehensive, covering the key aspects of IC design and providing the fundamental knowledge for students.

In the remaining program, the International Workshop on Integrated Circuits and Systems 2023 was organized at Vietnam National University, Hanoi campus with more than 35 attendees from both universities and industries. Various technical talks on sharing novel ideas, achievements, experimental results, and innovative applications on integrated circuits and systems for medical applications, Internet of Things (IoTs), Smart Cities, and Digital Transformation, etc.

Prepared by

Duy-Hieu Bui and Xuan-Tu Tran

_________________

Electro-Quest, Circuit Junxtion, and Introduction to HDL by IEEE CASS Madras Chapter

Electro-Quest

On May 6, 2024, Sri Sairam Engineering College and the IEEE Circuits and Systems Society hosted Electro-Quest for students as a part of the 75th Anniversary Global Celebration. Ms. S. Usha, Advisor of the IEEE Circuits and Systems Society, commenced the event with a Welcome Address, highlighting the achievements, advancements, and impact of circuits and systems technologies. She underscored the significance of networking and collaboration in mastering circuitry, noting that the event was exclusively for IEEE CAS Student members.

Ten teams were chosen from the preliminary round to compete in the final round of the event. The program was expertly run by student coordinators, who also made sure that the winners were properly acknowledged. The participant's job was to use TinkerCAD to simulate a given circuit.

Generous sponsorship from the management facilitated the prize distribution, with refreshments also being provided to all participants. We extend our gratitude to our CEO, Principal, Dean (Academics), and HOD-ECE Dr. J. Raja for their unwavering support and guidance, which contributed significantly to the successful conclusion of this contest.

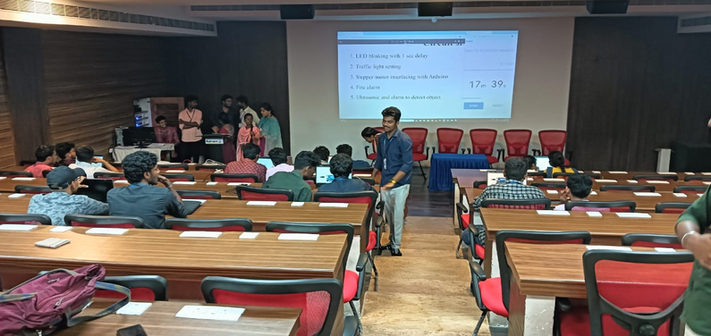

Circuit Junxtion

On May 2, 2024, Sri Sairam Engineering College and the IEEE Circuits and Systems Society hosted Circuit Junxtion for students as a part of the 75th Anniversary Global Celebration Ms. S, Usha, Advisor, IEEE Circuits and Systems Society, started with the Welcome Address and briefed about the achievements, advancements, and impact of circuits and systems technologies and also emphasized the importance of networking and collaboration in mastering circuitry. This event is exclusively conducted for IEEE CAS Student members.

A preliminary round was conducted and 10 teams were selected for the final round. Student coordinators organized the program well and the winners were selected. The management sponsored the prize amount. The prize amount was given on 03.05.24 by Prof. S. Sumathi.

A sincere gratitude to all participants and organizers for making Circuit Junxtion a resounding success and encouraging everyone to continue striving for excellence in their circuit mastery journey. We extend our gratitude to our CEO, Principal, Dean (Academics), and HOD-ECE Dr. J. Raja for their unwavering support and guidance, which contributed significantly to the successful conclusion of this contest.

Introduction to HDL

On April 25, 2024, Sri Sairam Engineering College and the IEEE Circuits and Systems Society conducted a workshop on Introduction to HDL for students as a part of the 75th Anniversary Global Celebration Ms. S, Usha, Advisor, IEEE Circuits and Systems Society. Ms. S. Usha, Associate Professor of the ECE department gave a talk on Introduction to HDL.

Hardware Description Language (HDL) is a specialized computer language that describes the structure and behavior of digital circuits. HDLs enable designers to model and simulate complex electronic systems before actual hardware implementation. Verilog and VHDL are two widely used HDLs, each with its syntax and features. HDLs allow for the creation of high-level abstractions, making it easier to design and verify digital circuits. They facilitate the design process by providing a systematic approach to describing hardware components and their interactions. Understanding HDL is essential for digital circuit designers and engineers involved in FPGA (Field-Programmable Gate Array) and ASIC (Application-Specific Integrated Circuit) design. Proficiency in HDLs enables efficient design iteration and reduces time-to-market for electronic products. Overall, HDLs play a crucial role in the design and development of modern digital systems, offering a powerful means of abstraction and simulation.

Ms. S. Usha thanked our CEO, Principal, Dean Academics, and HOD-ECE, HOD-CSE(IOT) for giving us this wonderful opportunity.

Provided by

Vishal Sakthi (CASS Chairperson), A. Swetha, and M. Bhavadharene