Our Editors-in-Chief’s Top Picks

The Editors-in-Chief of our CASS publications have selected some noteworthy papers from the recent issues of our journals:

IEEE Open Journal of Circuits and Systems

Paper 1

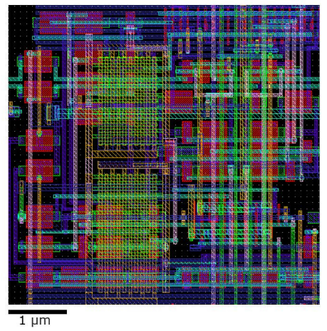

A Sub-mW Cortex-M4 Microcontroller Design for IoT Software-Defined Radios

Summary: This paper presents an Internet-of-Things (IoT) software-defined radio platform based on an ultra low-power microcontroller. The authors propose an ultra low-power microcontroller architecture with an ARM Cortex-M4 processor for the protocol-specific computations and a hardware digital front-end for the generic signal processing. The proposed architecture has been prototyped in 28nm FDSOI and the physical layers of the well-known LoRa and Sigfox protocols have been implemented in software.

Paper 2

An Efficient K-Best MIMO Detector for Large Modulation Constellations

Summary: This paper presents a sorter-free detection algorithm, where the K surviving nodes can be obtained in log2K iterations, which is independent of modulation size. Implementation results show that the proposed K-best MIMO detector supports a 6.4Gb/s throughput that has a 0.32 μs latency in a 90 nm process for a 256-quadrature amplitude modulation (QAM) 4 × 4 MIMO system.

Paper 3

A Brief Tutorial on Mixed Signal Approaches to Combat Electronic Counterfeiting

Summary: This paper introduces a variety of mixed-signal approaches to combat electronic counterfeiting. An LDO-based odometer capable of accurately classifying ICs as new or aged is presented as a promising method for detecting counterfeit and recycled ICs. Additionally, this paper discusses the use of physical unclonable functions (PUFs) as primitives for generating cryptographic keys for digital signatures, encryption, or authentication.

IEEE Transactions on Circuits and Systems II: Express Briefs

Paper 1

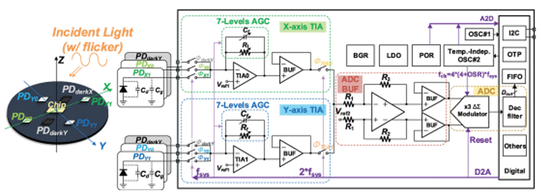

Y. Li , Z. Lin, W. Dong, Z. Hu, C. Wang, S. Zhuo, Y. Wu, H. Yu and P. Y. Chiang, “32-ppm/◦C Temperature-Independent Flicker Detection”, IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 71, no. 2, pp. 537-541, Feb. 2024. doi: 10.1109/TCSII.2023.3311090. https://ieeexplore.ieee.org/document/10237309

Summary: This paper outlines a light sensor that is not affected by the angle of incidence and has a wide dynamic range up to 138dB, equipped with a four-channel system for detecting flicker without being influenced by temperature changes, by a time-interleaved structure that utilizes two trans-impedance amplifiers and a 16-bit third-order incremental delta-sigma ADC. The design achieves angle insensitivity through a configuration of dual photodiodes arranged for both the X and Y axes. Testing results indicate that the sensor maintains a consistent angular response from −30° to 30° and has a field-of-view of ±67°, with a stable flicker detection and a temperature coefficient of 32ppm/°C within a temperature range of −30°C to 85°C.

Paper 2

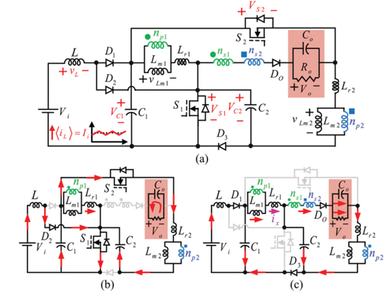

H. S. Gohari, S. Abbasian, N. A. Mardakheh, K. Abbaszadeh and F. Blaabjerg, “Coupled Inductor-Based Current-Fed Ultra-High Step-Up DC-DC Converter Featuring Low Input Current Ripple”, IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 71, no. 2, pp. 887-891, Feb. 2024. doi: 10.1109/TCSII.2022.3206231. https://ieeexplore.ieee.org/document/9888768

Summary: This paper introduces a DC-DC converter that achieves an exceptionally high voltage gain. The inclusion of two double-winding coupled inductors in the design allows for increased flexibility due to variable turn ratios. The converter’s simplicity is further enhanced by the simultaneous activation of its two switches, which simplifies both operation and control, requiring only a single gate pulse for the switch. A 200 W prototype of the converter has been constructed for laboratory testing, with experimental results provided to validate its performance.

Paper 3

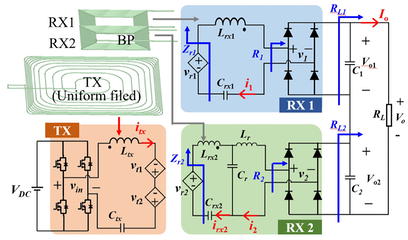

Z. Li, G. Ning, K. Zhao, H.Wang, Y. Liu, M. Fu, “A Dual-Mode Wireless Charger Based on Cascaded Rectifier and Hybrid Compensation”, IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 71, no. 3, pp. 1466-1470, Mar. 2024. doi: 10.1109/TCSII.2023.3321399. https://ieeexplore.ieee.org/document/10268969

Summary: A new wireless charger has been implemented in this paper, featuring a dual-mode operation through the integration of hybrid compensations and cascaded rectifiers. By examining the resonant tank's alternating current properties via a circuit model, it's possible to pinpoint the essential load resistance and elucidate the operational principles of both standard and protective modes. The showcased 30-W system maintains a consistent voltage output and a 92% efficiency, with a fast transient response time of 27 for its inherent overload protection feature.

IEEE Journal of Emerging and Selected Topics in Circuits and Systems

Paper 1

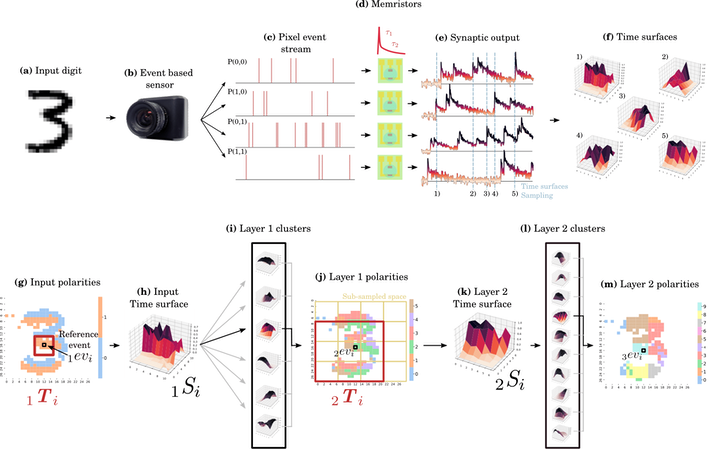

M. Rasetto, Q. Wan, H. Akolkar, F. Xiong, B. Shi and R. Benosman, "Building Time-Surfaces by Exploiting the Complex Volatility of an ECRAM Memristor," in IEEE Journal on Emerging and Selected Topics in Circuits and Systems, vol. 13, no. 4, pp. 877-888, Dec. 2023, doi: 10.1109/JETCAS.2023.3330832

Summary: Neuromorphic systems promise to accelerate low-power AI applications on the edge, but processing events requires complex circuit designs. In this work, the authors show how volatile properties of memristors can be used to process events in a neuromorphic architecture called Hierarchy of Time-Surfaces (HOTS) on visual classification tasks. Their results show how memristors could be used in the future as a compact do-it-all solution for future neuromorphic systems!

Paper 2

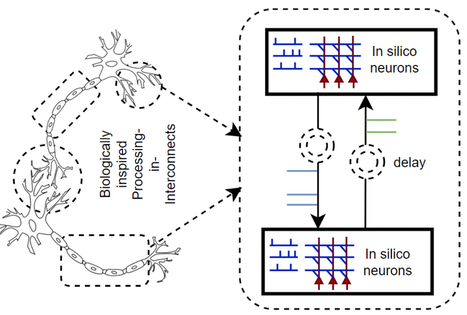

R. M. Srivatsav, S. Chakrabartty and C. S. Thakur, "Neuromorphic Computing With Address-Event-Representation Using Time-to-Event Margin Propagation," in IEEE Journal on Emerging and Selected Topics in Circuits and Systems, vol. 13, no. 4, pp. 1114-1124, Dec. 2023, doi: 10.1109/JETCAS.2023.3328916.

Summary: In this paper we show how address-event-representation (AER) can be used for implementing a processing-in-interconnect paradigm (Π2), similar to the concept of dendritic computing. The key novelty in this work is the time-to-event margin propagation (TEMP) principle that can exploit computational primitives like causality, sorting and triggering which can be naturally mapped onto the physics of an interconnect (physical or virtual) and enable event-based communications. We demonstrate how TEMPbased spiking neural networks can produce a rich repertoire of spatio-temporal dynamics that can be used for building energy-efficient AI hardware.

Paper 3

B. V. Benjamin, R. L. Smith and K. A. Boahen, "A Low Thermal Sensitivity Subthreshold-Current to Pulse-Frequency Converter for Neuromorphic Chips," in IEEE Journal on Emerging and Selected Topics in Circuits and Systems, vol. 13, no. 4, pp. 956-964, Dec. 2023, doi: 10.1109/JETCAS.2023.3321105.

Summary: To convert a subthreshold current to a pulse frequency efficiently and predictably, a silicon soma that conserves energy with current feedback and lessens thermal sensitivity with voltage feedback is presented in this paper. By successfully combining current feedback with voltage feedback, the soma proposed in this paper is 10-fold less sensitive to temperature than a previous current-feedback-only design that uses 7.6-fold more silicon area. This advance allowed a mixed-signal neuromorphic chip to be predictably programmed for the first time.

IEEE Transactions on Very Large Scale Integration (VLSI) Systems

Paper 1

A. Mitrovic and E. G. Friedman, "Thermal Exploration of RSFQ Integrated Circuits," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 32, no. 4, pp. 728-738, April 2024, doi: 10.1109/TVLSI.2023.3348452.

Summary: This paper discusses the development of advanced design and analysis capabilities for rapid single flux quantum (RSFQ) circuits in order to transition them to a VLSI-complexity technology. Specifically, the paper addresses the need for thermal analysis methodologies due to the temperature sensitivity of RSFQ circuits, which can affect the Josephson critical current density and the superconductivity of interconnects. A methodology for assessing the thermal properties of RSFQ integrated circuits is introduced, including a thermal model and a multistage partitioning algorithm. This algorithm partitions the circuit based on its layout into blocks, applies an average thermal model for simulation, and identifies potential hot spots using a threshold temperature for functional failure. A peak thermal model was also developed to detect these hot spots. The authors tested their methodology on complex blocks and validated with numerical solvers showing less than 1% error. They applied it to a AMD2901 benchmark circuit, producing a thermal profile in under 68 minutes.

Paper 2

Z. Lu et al., "An RRAM-Based Computing-in-Memory Architecture and Its Application in Accelerating Transformer Inference," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 32, no. 3, pp. 485-496, March 2024, doi: 10.1109/TVLSI.2023.3345651.

Summary: This paper outlines challenges in running deep neural network (DNN)-based transformer models on power-constrained edge devices due to their memory-intensive attention mechanisms. An emerging solution is computing-in-memory (CIM), which minimizes data movement by performing computations directly within memory cells. However, traditional CIM designs struggle with high-precision tasks needed for NLP applications, like floating-point operations, and require complex control systems and expensive peripheral circuits. To address this, the paper introduces a scalable, RRAM-based in-memory architecture named RIME, designed for floating-point operations using single-cycle logic gates. RIME optimizes the data flow with parallel and pipeline processing and simplifies the control and peripheral circuitry, enhancing efficiency. It includes pipelined implementations for critical operations like matrix multiplication and the softmax function, forming the basis of a transformer model accelerator. Experimental comparisons show that the RIME-based accelerator significantly outperforms GPU implementations in terms of timing and energy efficiency, without losing accuracy in inference tasks.

Paper 3

T. Zhang, M. Tehranipoor and F. Farahmandi, "TrustGuard: Standalone FPGA-Based Security Monitoring Through Power Side-Channel," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 32, no. 2, pp. 319-332, Feb. 2024, doi: 10.1109/TVLSI.2023.3335876.

Summary: This paper discusses the security challenges in the Internet of Things (IoT) era, particularly focusing on cyber-attacks like malware intrusions that compromise IoT devices. Traditional detection solutions at the operating-system or hardware level are often inadequate, either slowing down performance significantly or being too costly. As an alternative, the paper introduces TrustGuard, a standalone security monitoring framework that uses side-channel analysis—specifically power consumption and electromagnetic emissions—to detect malware. TrustGuard integrates this detection capability with machine learning algorithms on a single field-programmable gate array (FPGA) platform, enhancing efficiency and reducing the need for external equipment like oscilloscopes. This system is implemented on the Xilinx ZCU104 platform and tested against the BeagleBone Black board. By profiling standard application behaviors and identifying anomalies due to attacks, TrustGuard demonstrates high efficacy, achieving over 90% accuracy in malware detection.

Paper 4

J. Nurmi, S. Aunet and A. Saberkari, "Guest Editorial Selected Papers From IEEE Nordic Circuits and Systems Conference (NorCAS) 2022," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 32, no. 1, pp. 1-3, Jan. 2024, doi: 10.1109/TVLSI.2023.3339268.

Summary: IEEE Transactions on VLSI does not generally publish special issues, but occasionally it publishes special sections from selected conferences in the VLSI area. The January 2024 TVLSI issue has such a special section composed of substantially extended handpicked papers from the IEEE Nordic Circuits and Systems Conference (NorCAS) 2022 that took place in October 2022 in Oslo, Norway.

IEEE Transactions on Circuits and Systems for Video Technology

Paper 1

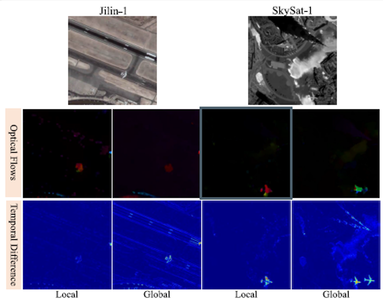

Yi Xiao, Qiangqiang Yuan, Kui Jiang, Xianyu Jin, Jiang He, Liangpei Zhang, and Chia-Wen Lin, “Local-Global Temporal Difference Learning for Satellite Video Super-Resolution,” IEEE Transactions on Circuits and Systems for Video Technology, VOL. 34, NO. 4, APRIL 2024. https://ieeexplore.ieee.org/document/10239514

Summary: This paper proposes to exploit the well-defined temporal difference for efficient and effective temporal compensation in satellite Video Super-Resolution (VSR). This approach aims to improve over optical-flow-based and kernel-based approaches that have been extensively explored for temporal compensation in satellite VSR, but are less generalizable in large-scale or complex scenarios, especially in satellite videos.

To fully utilize the local and global temporal information within frames, the short-term and long-term temporal discrepancies are systematically modeled since these discrepancies offer distinct and mutually complementary properties. Specifically, a Short-term Temporal Difference Module (S-TDM) is designed to extract local motion representations from RGB difference maps between adjacent frames, which yields more clues for accurate texture representation. To explore the global dependency in the entire frame sequence, a Long-term Temporal Difference Module (L-TDM) is proposed, where the differences between forward and backward segments are incorporated and activated to guide the modulation of the temporal feature, leading to a holistic global compensation. Furthermore, a Difference Compensation Unit (DCU) is proposed to enrich the interaction between the spatial distribution of the target frame and temporal compensated results, which helps maintaining spatial consistency, while refining the features to avoid misalignment. Objective and subjective evaluations conducted across five mainstream video satellites demonstrate the method proposed in this work performs favorably against state-of the-art approaches. The code is available at https://github.com/XY-boy/LGTD.

In summary, the main contributions of this paper are:

- It generalizes the idea of temporal difference to achieve temporal compensation for satellite VSR. The proposed local-global temporal difference learning is computation-friendly, thus providing an alternative to optical flows.

- The proposed S-TDM and L-TDM could systematically utilize both short-term and long-term temporal complementary information from local and global motion patterns.

- A Difference Compensation Unit (DCU) is designed to alleviate misalignment in temporal difference learning and to help TMDs focus on capturing temporal information that is beneficial to satellite VSR.

- Compared with optical-flow-based and kernel-based approaches, the method proposed in this work achieves favorable quantitative and qualitative results on five mainstream video satellites.

Figure (left): Comparison between RGB temporal differences and optical flow maps. Temporal differences activate more accurate and sharp cues than optical flows. The local temporal difference and global temporal difference are not equally informative as they reflect a different level of difference.

Paper 2:

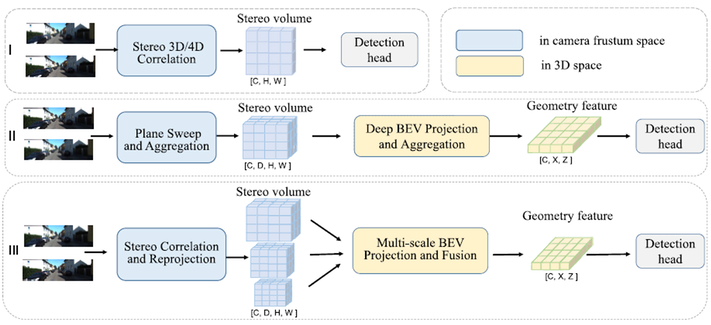

Aqi Gao, Yanwei Pang, Jing Nie, Zhuang Shao, Jiale Cao, Yishun Guo, and Xuelong Li, “ESGN: Efficient Stereo Geometry Network for Fast 3D Object Detection,” IEEE Transactions on Circuits and Systems for Video Technology, VOL. 34, NO. 4, APRIL 2024. https://ieeexplore.ieee.org/document/9869894

Summary: This paper proposes an efficient stereo geometry network (ESGN) aiming to solve the inferior accuracy of fast stereo-based 3D object detectors, which is argued to depend on poor geometry-aware feature representation in 3D space. To solve this problem, the key design choice in the proposed ESGN is an efficient geometry-aware feature generation (EGFG) module. This module first uses a stereo correlation and reprojection operation to construct multi-scale stereo volumes in camera frustum space, then employs a multi-scale bird’s eye view (BEV) projection and fusion module to generate multiple geometry-aware features. In these two steps, deep multi-scale information fusion is used for discriminative geometry-aware feature generation, without any complex aggregation network. In addition, a deep geometry-aware feature distillation scheme is introduced to guide stereo feature learning with a LiDAR-based detector. Experiments are performed on the KITTI dataset, where ESGN outperforms the fast state-of-art-art detector YOLOStereo3D by 5.14% on mAP3d at 62ms. ESGN is claimed to achieve a best trade-off between accuracy and speed.

In summary, the main contributions of this work are:

• An efficient stereo geometry-aware feature network (ESGN) is proposed for fast 3D object detection. The key module is an efficient geometry-aware feature generation (EGFG) module. EGFG extracts discriminative geometry-aware features in 3D space by adopting deep multi-scale information fusion in both stereo volume and geometry-aware feature generations.

• A deep geometry-aware feature distillation (DGFD) scheme is introduced. DGFD uses a LiDAR-based detector to extract multi-level geometry-aware features and employs these features to guide stereo feature learning.

• Experiments on the KITTI dataset, show on the moderate test set an AP3d of 46.39% at a speed of 62ms, which represents an optimal trade-off between accuracy and speed. Compared to fast YOLOStereo3D, ESGN provides an absolute gain of 5.14% at a comparable speed.

Figure (above): Comparison of different stereo methods. (I) Camera frustum space-based method YOLOStereo3D. It uses a stereo 3D/4D correlation module to generate stereo volume in camera frustum space for 3D detection, which faces the issue of object distortion. (II) Voxel based method DSGN: In the steps of stereo volume and geometry-aware feature generations, it adopts the heavy 3D and 2D aggregation networks, resulting in a slow speed. (III) The efficient stereo geometry-aware network (ESGN) proposed in this work: Compared to the DSGN voxel-based method, the ESGN proposed in this paper adopts deep multi-scale information fusion, instead of heavy 3D and 2D aggregation networks, for geometry-aware feature generation.

Paper 3:

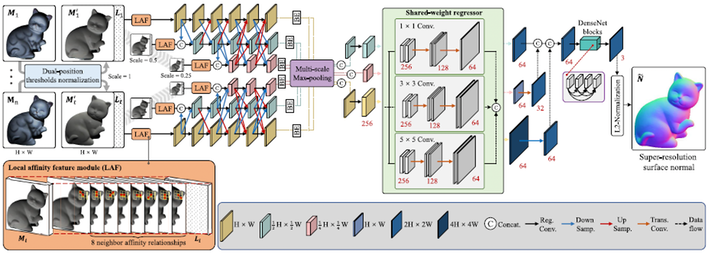

Yakun Ju, Muwei Jian, Cong Wang, Cong Zhang, Junyu Dong, and Kin-Man Lam, ”Estimating High-Resolution Surface Normals via Low-Resolution Photometric Stereo Images,” IEEE Transactions on Circuits and Systems for Video Technology, VOL. 34, NO. 4, APRIL 2024. https://ieeexplore.ieee.org/document/10208243

Summary: Measuring high-resolution surface normals via low-resolution photometric stereo images is of great importance. This paper proposes a Super-resolution Photometric Stereo Network, namely SR-PSN that aims to address the issues of measuring the high-resolution surface normals from low-resolution photometric images. To this end, the method proposed in this work: (1) applies a dual-position threshold normalization pre-processing scheme to effectively handle the spatially-varying reflectance of non-Lambertian surfaces, (2) adopts a local affinity feature module to learn the rich structural representation by explicitly revealing the neighbor relationships, (3) employs a parallel multi-scale feature extractor, which preserves high-resolution representations and deep feature extraction, and (4) proposes a shared-weight regressor to handle the multi-scale features, to prevent the model collapsing into learning non-important features related to a certain fixed scale. Extensive ablation experiments presented in the paper validate the effectiveness of the proposed modules. Quantitative experiments conducted on public benchmarks demonstrate that SR-PSN outperforms state-of-the-art calibrated photometric stereo methods. Notably, SR-PSN achieves superior results, while utilizing photometric stereo images with only half the resolution of other methods. It effectively restores the structure of complex surfaces, producing a high-resolution normal map.

Figure (above): The overall structure of the proposed SR-PSN. It includes: a dual-position thresholds normalization, a local affinity feature module (LAF), a multi-scale feature extractor, a bilateral extraction module (BE), and a shared-weighted feature regressor.

______________________________

CAll for Papers: TCAS-I Special Issue on Emerging Hardware Security and Trust Technologies

Manuscript submission deadline: 1 May 2024

Hardware security and trust have become a pressing issue during the last two decades due to the globalization of the semiconductor supply chain and ubiquitous network connection of computing devices. In addition to software, hardware circuits and systems are now an attractive attack surface for launching powerful cross-layer security attacks, allowing attackers to infer secret information, hijack control flow, compromise system root-of-trust, steal intellectual property, and fool machine learners. Hardware security threats can arise during various stages of the entire circuit life cycle, ranging from specification, design to fabrication and even recycling, which make the hardware security uniquely challenging.

The purpose of this special issue is to effectively convey the most up-to-date topics in the hardware security community. Topics of interest for this special issue lies in the introduction of most recent security attacks and threat models that are discovered in the hardware design and supply chain, emerging applications, as well as circuit theory, design methodology, design tools and implementations that help to thwart these threats. We sincerely hope not only this special issue can be a valuable reference for the target readers and researchers in the hardware security community, but also can motivate researchers in circuit and system design and in emerging technologies such as 5G/6G, IoT and artificial intelligence, to consider the new challenges and opportunities of incorporating an additional dimension of security into robust circuit and system design, testing, verification and implementation.

Hardware security is a fashionable research area in both industry and academy. Its scope is consistently growing. This special issue will include papers from extended version of AsianHOST 2023 and it also opens to public submissions related to emerging hardware security and trust technologies.

Authors are invited to submit Regular papers following the IEEE Transactions on Circuits and Systems I: Regular Papers (TCAS-I) guidelines within the scope of this Special Issue. Topics in scope for “Emerging Hardware Security and Trust Technologies” include (but are not limited to):

- Hardware-intrinsic security primitives (e.g., PUF and TRNG)

- Architectural and microarchitectural attacks and defenses

- Secure system-on-chip (SoC) architecture

- Post-quantum cryptography (PQC) implementation

- Trusted platform modules and hardware virtualization

- Side-channel attacks and countermeasures

- Hardware Trojan attacks and detection techniques

- Security analysis and protection of Internet of Things (IoT)

- Hardware IP core protection and trust for consumer electronics systems and IoT

- Security and trust of machine learning and artificial intelligence

- Automobile, self-drive, and autonomous vehicle security

- 5G and physical layer security

- Hardware-assisted cross-layer security

- Cyber-physical system (CPS) security and resilience

- Metrics, policies, and standards related to hardware security

- Security verification at IP, IC, and system levels

- Reverse engineering and hardware obfuscation

- Supply chain risks mitigation including counterfeit detection & avoidance

- Trusted manufacturing including split manufacturing, 2.5D, and 3D ICs

- Emerging nanoscale technologies in hardware security applications

Submission procedure:

Manuscripts should be prepared following the TCAS-I Information for Authors, which can be found here, and submitted through the IEEE author portal here.

Please choose the option “Special Issue on Emerging Hardware Security and Trust Technologies” in your submission.

Please note that papers submitted to TCAS-I are expected to be typically of 9-11 pages and no more than 14 pages in length in the two-column IEEE Transactions format. Please read the Information for Authors regarding mandatory overlength page charges beyond 11 pages.

Please be aware that the submitted paper will undergo the standard review process to ensure that all the contributions meet the high standards of the Journal. In this regard, if a conference paper has been previously published, your submission to this special issue must be a significantly more complete version of your conference contribution with appropriate addition of experimental data or other relevant verification. As a rule of thumb, you should add at least 70% more unpublished technical material. When submitting the extended journal version of your conference paper, you must disclose the original conference paper and attach a letter explicitly highlighting the additional contributions of the TCAS-I paper relative to the original conference paper.

Important dates

- 1 May 2024: Paper submission

- 15 June 2024: First-round review due

- 30 July 2024: Revised manuscript submission

- 20 August 2024: Second round review due

- 10 September 2024: Second (minor) revised paper submission

- 30 September 2024: Guest editor's final recommendation

- 15 October 2024: Final accepted paper submission due

- 31 December 2024: Expected inclusion in issue

Guest Editors:

- Qiang Liu, Tianjin University, China

- Weiqiang Liu, Nanjing University of Aeronautics and Astronautics, China

- Chongyan Gu, Queen's University Belfast, U.K

- Reza Azarderakhsh, Florida Atlantic University, U.S.A.

______________________________

Latest Tables of Contents of CAS Sponsored Journals

The latest issues of our CAS sponored journals have been published and the tables of contents can be accessed through the following links:

- IEEE Transactions on Circuits and Systems I: Regular Papers

- IEEE Transactions on Circuits and Systems II: Express Briefs

- IEEE Transactions on Circuits and Systems for Video Technology

- IEEE Journal on Emerging and Selected Topics in Circuits and Systems

- IEEE Circuits and Systems Magazine

- IEEE Transactions on Biomedical Circuits and Systems

- IEEE Design and Test Magaz

- IEEE Open Journal of Circuits and SystemsYongxiang Y