TECHNOLOGY NEWS

Reconfigurable Architectures for Imaging: From Algorithm to Power Modeling on FPGAs

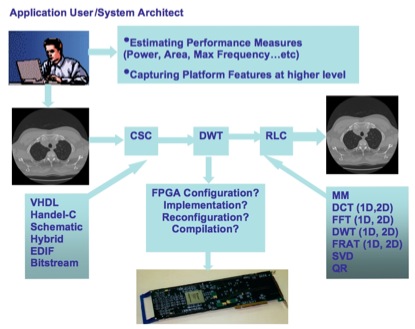

Reconfigurable computing has recently demonstrated huge power and performance gains on data and computationally intensive applications. Field Programmable Gate Arrays (FPGAs) have been evolving and improving rapidly, and have consistently shown the fastest rates of performance gains. While capacity doubling in CPUs occurs every 18 months, in line with the prediction of the well known Moore’s Law, the performance of FPGAs increases at an even more rapid rate of four times every two years. FPGA design tools have reached considerable levels of maturity in a short span of time but a lot of work remains to be done in the area of high level power estimation which needs to be integrated into the design cycle of highly reconfigurable architectures for applications such as imaging. Research carried out recently by the author and his research team has involved the development and implementation of efficient parametrizable IP cores for matrix algorithms, as illustrated in the figure below, used in imaging applications such information retrieval and medical image segmentation.

Figure on left: Reconfigurable environment and IP cores generator for imaging

The IP cores generated have been implemented efficiently on the different virtex FPGA chips and a speed-up of 10-20 times compared to efficient MATLAB implementation has been achieved. Two applications have been recently targeted in medical image segmentation for tumour tracking and detection for radiotherapy planning and cancer diagnosis and latent semantic indexing used in information retrieval. Multiresolution IP cores including discrete wavelet transform and finite ridglet transform have developed for the two applications with better performances compared to existing architectures and systems in place. Also an electronic nose application has been targeted in collaboration with the University of Science and Technology Hong Kong, where the author and his research team have implemented a number of pattern recognition algorithm on FPGA for gas detection and classification.

The team has also integrated in the reconfigurable environment a novel functional level power analysis and modeling FLPAM tool for FPGA.

The underlying concept of FLPAM is to build a mathematical model that incorporates all the system variables, enabling the user to perform high level estimation of the power and energy metrics of the core for a given set of parameters early on in the design cycle itself. The steps involved in building the power model for different IP cores are as follows:

1. Create a power chart by measuring power for each individual component of Dynamic Power (DP), i.e. signal, logic, clock, I/O;

2. Identify all variables in the system, including user customizable ones, and internal system parameters, e.g. frequency, vector length, area and voltage;

3. Deduce the order and number of terms in each equation from the logic resources used, and the various parameters involved in the design. In the case of FPGAs, each individual component of power is modeled separately, and all the models are added together to yield a global power model. The order of the equation, and the constant coefficients associated with each variable are unknown parameters. This step is essentially about choosing a model;

4. Derive the coefficients for each individual power component by performing non-linear regression analysis on the data in power chart for fitting the system variables;

5. Optimize the design by iterative analysis of the influence of design modifications on power and energy metrics until convergence has been achieved; and

6. Determine optimum operational parameters of the final model through constrained multivariate techniques.

Ongoing research is focusing on the design and implementation of novel reconfigurable architectures for distributed wireless sensors used in imaging and addressing the problem of processing very large data and matrices using different design approaches and arithmetic techniques. A range of applications will be tackled and accelerated on reconfigurable hardware including biometrics, information retrieval, medical image compression and segmentation, and computational finance using image processing techniques.

Abbes Amira, Electronic and Computer Engineering, Brunel University, UK (Email: abbes.amira@brunel.ac.uk)

_____________________________

This article was recommended by Andreas Demosthenous.